#### **Major Project Report on**

# DESIGN AND VERIFICATION OF VENDING MACHINE USING VERILOG HDL

Submitted in partial fulfilment of the requirement for the award of degree of

#### **BACHELOR OF TECHNOLOGY IN**

#### **ELECTRONICS AND COMMUNICATION ENGINEERING**

SUBMITTED BY

OBINENI NITHIN 218R1A04N9

PAGIDIMARRI PRAVEEN 218R1A04O0

PANJALA KISHORE 218R1A04O1

PAPPU PURNACHANDU 218R1A04O2

Under the Esteemed Guidance of

Ms. L. LAVANYA Assistant Professor

#### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

## **CMR ENGINEERING COLLEGE**

### **UGC AUTONOMOUS**

(Approved by AICTE, UGC AUTONOMOUS, Accredited by NBA, NAAC) Kandlakoya(V), Medchal(M), Telangana.

(2024-2025)

## **CMR ENGINEERING COLLEGE**

#### **UGC AUTONOMOUS**

(Approved by AICTE, UGC AUTONOMOUS, Accredited by NBA, NAAC) Kandlakoya (V), Medchal, Telangana.

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

#### **CERTIFICATE**

This is to certify that Major-project work entitled "DESIGN AND VERIFICATION OF VENDING MACHINE USING VERILOG HDL" is being submitted O. NITHIN bearing Roll No 218R1A04N9, P. PRAVEEN bearing Roll No 218R1A04O0, P. KISHORE bearing Roll No 218R1A04O1, P. PURNA CHANDU bearing Roll No 218R1A04O2 in B. Tech IV-II semester, Electronics and Communication Engineering is a record Bonafide work carried out by then during the academic year 2024-25. The results embodied in this report have not been submitted to any other University for the award of any degree.

Ms. L. LAVANYA

HEAD OF THE DEPARTMENT

Dr. SUMAN MISHRA

**EXTERNAL EXAMINER**

#### **ACKNOWLEDGEMENTS**

We sincerely thank the management of our college **CMR Engineering College** for providing required facilities during our project work. We derive great pleasure in expressing our sincere gratitude to our Principal **Dr. A. S. Reddy** for his timely suggestions, which helped us to complete the project work successfully. It is the very auspicious moment we would like to express our gratitude to **Dr. SUMAN MISHRA**, Head of the Department, ECE for his consistent encouragement during the progress of this project.

We take it as a privilege to thank our project coordinator **Dr. T. SATYANARAYANA**, Associate Professor, Department of ECE for the ideas that led to complete the project work and we also thank him for his continuous guidance, support and unfailing patience, throughout the course of this work. We sincerely thank our project internal guide **Ms. L. LAVANYA**, Assistant Professor of ECE for guidance and encouragement in carrying out this project work.

#### **DECLARATION**

We hereby declare that the major project entitled "DESIGN AND VERIFICATION OF VENDING MACHINE USING VERILOG HDL" is the work done by us in campus at CMR ENGINEERING COLLEGE, Kandlakoya during the academic year 2024-2025 and is submitted as Major project in partial fulfilment of the requirements for the award of degree of BACHELOR OF TECHNOLOGY in ELECTRONICS AND COMMUNICATION ENGINEERING FROM JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY, HYDERABAD.

O. NITHIN (218R1A04N9)

P. PRAVEEN (218R1A04O0)

P. KISHORE (218R1A04O1)

P. PURNA CHANDU (218R1A04O2)

#### **ABSTRACT**

The design, implementation, and verification of a vending machine using the Finite State Machine (FSM) methodology in Verilog HDL. The FSM is used to manage the multiple states of the vending machine, including "idle," "accepting coins," "dispensing item," and "returning change." The implementation of the vending machine is done in Verilog HDL, and the FSM is implemented as a state diagram. The design is then synthesized using the Genus synthesis tool and implemented using the Encounter implementation tool. The Genus tool uses advanced optimization techniques, such as timing-driven placement and clock tree synthesis, to improve the design's performance and area. The Encounter tool performs physical design, including placement and routing, to meet the design's timing, power, and area constraints. To validate the design's correctness and functionality, a test bench is created to simulate the behavior of the vending machine. The simulation results are then used to verify that the design meets the required specifications and that the FSM behaves as expected. The proposed design is then can be implemented on a Field Programmable Gate Array (FPGA) to demonstrate its effectiveness in a real-world scenario. The results of the implementation are presented and analyzed to validate the design's performance, power consumption, and area. Overall, the vending machine using FSM in Verilog HDL, implemented in Genus and Encounter, provides a reliable and efficient solution for users to purchase items from the machine. The proposed design and implementation demonstrate the feasibility and effectiveness of this approach, and the results show that the design meets the required specifications and performs well in a real-world scenario.

### **CONTENTS**

| CHAPTERS                     | PAGI |

|------------------------------|------|

| CERTIFICATE                  | I    |

| ACKNOWLEDGEMENT              | II   |

| DECLARATION BY THE CANDIDATE | III  |

| ABSTRACT                     | IV   |

| CONTENTS                     |      |

| LIST OF FIGURES              | VII  |

| CHAPTER-1                    |      |

| 1. INTRODUCTION              | 01   |

| 1.1 INTRODUCTION             |      |

| 1.2 OBJECTIVE                | 02   |

| 1.3 OVERVIEW OF THE PROJECT  | 03   |

| CHAPTER-2                    |      |

| 2. LITERAURE SURVEY          |      |

| 2.1 EXISTING SYSTEM          | 05   |

| 2.2 PROPOSED SYSTEM          | 08   |

| 2.3 INTRODUCTION TO VLSI     | 11   |

| 2.3.1 VLSI Technology        | 11   |

| 2.3.2 Why VLSI               | 13   |

| 2.3.3 Structured design      | 16   |

| 2.3.4 Applications of VLSI   | 17   |

| 2.3.5 ASIC                   | 18   |

| 2.3.6 ASIC design flow       | 19   |

| CHAPTER-3                    |      |

| 3. SOFTWARE REQUIREMENTS     |      |

| 3.1 XILINX ISE               | 21   |

| 3.2 XILINX ISE 13.2i         | 21   |

| 3.2.1 SIMULATION             | 21   |

| 3.2.2 SYNTHESIS              | 21   |

| 3.2.3 PROCEDURE              | 22   |

| 3.3 PROCEDURE FOR SYNTHESIS  | 22   |

| 3.4 VIVADO SOFTWARE          | 31 |

|------------------------------|----|

| CHAPTER-4                    |    |

| WORKING OF THE PROJECT       |    |

| 4.1 WORKING OF THE PROJECT   | 43 |

| CHAPTER-5                    |    |

| RESULTS                      |    |

| 5.1 RESULTS OF THE PROJECT   | 47 |

| 5.2 APPLICATIONS             | 52 |

| 5.3 ADVANTAGES               | 52 |

| CHAPTER-6                    |    |

| 6. CONCLUSION & FUTURE SCOPE |    |

| CONCLUSION                   | 53 |

| FUTURE SCOPE                 | 54 |

| REFERENCES                   | 56 |

| APPENDIX                     | 57 |

## LIST OF FIGURES

|             |                                                    | PAGE |

|-------------|----------------------------------------------------|------|

| Figure 2.1  | SIMPLIFIED VENDING MACHINE ARCHITECTURE            | 09   |

| Figure 2.2  | FLOW CHART                                         | 10   |

| Figure 2.3  | ASIC DESIGN                                        | 19   |

| Figure 2.4  | ASIC DESIGN FLOW                                   | 19   |

| Figure 3.1  | CREATING NEW FILE IN XILINX                        | 23   |

| Figure 3.2  | DISPLAYS ONE MORE DAILOG BOX FOR SPECIFICATIONS    |      |

|             | IN XILINX                                          | 24   |

| Figure 3.3  | DISPLAYS AGAIN A DAILOG BOX AS SHOWN BELOW         |      |

|             | WITH THE CREATED PROJECT DESCRIPTION IN XILINX     | 24   |

| Figure 3.4  | SPECIFIED NAME IN CREATED THEN CREATED THE VERILOG |      |

|             | FILE IN THE PROJECT                                | 24   |

| Figure 3.5  | SELECT NEW SOURCE THE IT DISPLAYS THE DIALOG BOX   |      |

|             | WHICH IS CONTAINING OF LIST OF FILE FORMAT         | 25   |

| Figure 3.6  | SELECT INPUTS & OUTPUTS AND INOUTS IN XILINX       | 26   |

| Figure 3.7  | DISPLAYS AGAIN A DAILOGBOX FIVING DETAILS OF       |      |

|             | FILENAME IN XILINX                                 | 26   |

| Figure 3.8  | OPEN A WHITE SPACE IN THE PROJECT WINDOW           |      |

|             | CONTAINING FILENAME IN XILINX                      | 27   |

| Figure 3.9  | WRITING CODE SELECT THE FILENAME IN XILINX         | 27   |

| Figure 3.10 | LIST FILES THEN SELECT FILE FOR WHICH WE ARE       |      |

|             | CREATING THE TESTBENCH IN XILINX                   | 28   |

| Figure 3.11 | LIST FILES THEN SELECT FILE FOR WHICH WE ARE       |      |

|             | CREATING THE TESTBENCH IN XILINX                   | 28   |

| Figure 3.12 | GIVE A TESTBENCH FILE IN THE PROJECT WINDOW        | 29   |

| Figure 3.13 | SELECT SIMULATION FROM THE VIEWBAR IN THE          |      |

|             | PROJECT WINDOW IN XILINX                           | 29   |

| Figure 3.14 | DOUBLE CLICK ON ISE SIMULATOR IN XILINX            | 30   |

| Figure 3.15 | CLICK ON SIMULATE BEHAVIOURAL MODEL IN XILINX      | 30   |

| Figure 3.16 | WAVEFORMS WINDOW HAVING OPTION TO ZOOMOUT &        |      |

|             | ZOOMIN IN XILINX                                   | 31   |

| Figure 3.17 | INTERFACE OF THE VIVADO SOFTWARE                   | 33   |

| Figure 3.18 | TO CREATE A PROJECT GO TO THE FILE AND CLICK ON  |    |

|-------------|--------------------------------------------------|----|

|             | THE PROJECT                                      | 34 |

| Figure 3.19 | CREATE PROJECT NAME                              | 35 |

| Figure 3.20 | SELECTING PROJECT TYPE                           | 35 |

| Figure 3.21 | ADDING FILE VIVADO                               | 36 |

| Figure 3.22 | SELECTING CODE IN VIVADO                         | 36 |

| Figure 3.23 | SELECTING THE DEFAULT PART                       | 37 |

| Figure 3.24 | SELECTING THE FINAL STEP OF PROJECT CREATING     | 37 |

| Figure 3.25 | PROJECT MANAGER OF VIVADO SOFTWARE               | 38 |

| Figure 3.26 | PROJECT SUMMARY OF VIVADO SOFTWARE               | 38 |

| Figure 3.27 | IN DESIGNING SOURCE SELECTING RUN SYNTHESIS      | 39 |

| Figure 3.28 | OPEN SYNTHESIZED DESIGN CLICK OK                 | 39 |

| Figure 3.29 | SYNTHESUZED DESIGN                               | 40 |

| Figure 3.30 | INSIDE SYNTHESIZED DESIGN                        | 40 |

| Figure 3.31 | SELECTING ON SCHEMATIC IN PROJECT SUMMARY        | 41 |

| Figure 3.32 | RUN SIMULATION AND SELECT BEHAVIOURAL SIMULATION | 41 |

| Figure 3.33 | FINAL PART IN THE VIVADO SIMULATION PART         | 42 |

| Figure 4.1  | WORKING BLOCK DIAGRAM                            | 43 |

| Figure 4.2  | FLOW CHART OF VENDING MACHINE                    | 45 |

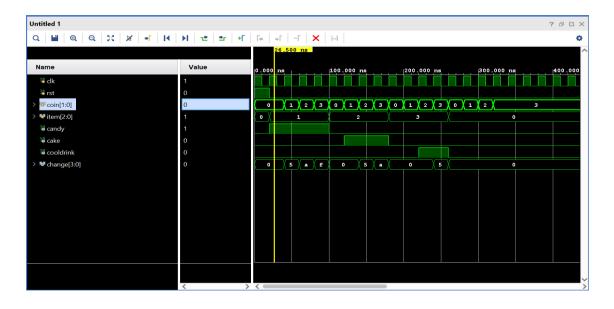

| Figure 5.1  | CASE 1                                           | 47 |

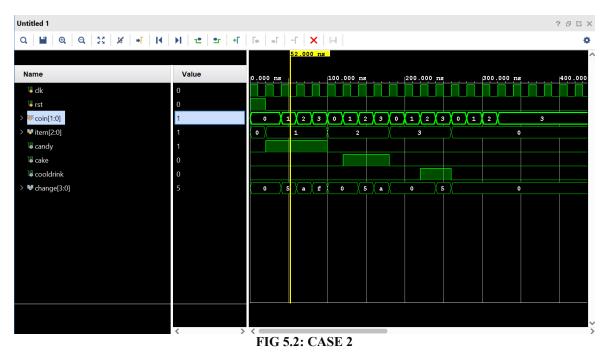

| Figure 5.2  | CASE 2                                           | 48 |

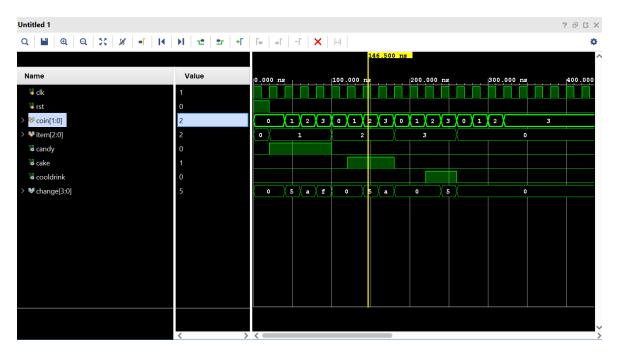

| Figure 5.3  | CASE 3                                           | 49 |

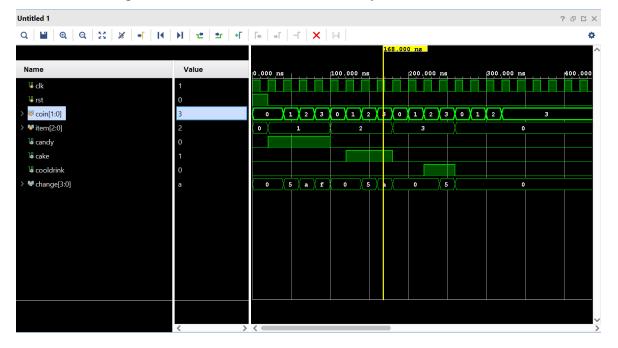

| Figure 5.4  | CASE 4                                           | 50 |

| Figure 5.5  | CASE 5                                           | 51 |

#### **CHAPTER 1**

#### INTRODUCTION

Vending machines have become an integral part of modern automated retail systems, providing quick and efficient delivery of products such as snacks, beverages, and other small items. These machines play a significant role in various locations, including offices, schools, hospitals, shopping malls, and transportation hubs, where they offer convenience and round-the-clock availability of goods. The primary advantage of vending machines is their ability to operate without human intervention, reducing operational costs and enhancing efficiency.

#### 1.1 INTRODUCTION

The functionality of a vending machine is controlled by an embedded system that processes user inputs, validates transactions, and dispenses selected items. These systems typically consist of multiple hardware and software components, including sensors, actuators, microcontrollers, and payment processing mechanisms. Advanced vending machines integrate cashless payment options, such as credit/debit cards, mobile wallets, and QR code scanning, improving accessibility and user experience.

To ensure reliability and accuracy, vending machines employ digital logic circuits to handle various operations, such as coin detection, product selection, and change dispensing. The implementation of these digital circuits requires precise design methodologies that guarantee smooth transaction processing and error-free operation. This has led to the adoption of Hardware Description Languages (HDLs) such as Verilog for designing and implementing vending machine controllers.

With the advancement of digital design techniques, Verilog HDL has gained popularity for modeling, simulation, and verification of digital circuits. It allows designers to develop efficient vending machine controllers that meet industry standards and operational requirements. Verilog HDL facilitates the implementation of finite state machines (FSMs) to manage different states of a vending machine, including idle, coin acceptance, product selection, transaction validation, and item dispensing, where they offer convenience and round-the-clock availability of goods. The primary advantage of vending machines is their ability to operate without human intervention, reducing operational costs and enhancing efficiency.

This project focuses on the design and verification of a vending machine using Verilog HDL. The system will be modeled as a finite state machine (FSM) to handle coin insertion, product selection, and item dispensing while ensuring correct transaction processing. The design will be thoroughly tested and verified using simulation techniques to validate its correctness, efficiency, and reliability. Through this project, a fully functional vending machine controller will be developed, demonstrating the application of digital design principles in real-world automated systems.

#### 1.2. OBJECTIVE

The objective of this project is to design, implement, and verify a digital vending machine using Finite State Machine (FSM) methodology in Verilog HDL. The vending machine is designed to handle multiple functions, including coin acceptance, item selection, dispensing, and returning change, ensuring smooth and efficient transactions.

#### 1. Design Implementation

The vending machine is implemented in Verilog HDL, a hardware description language suitable for designing digital circuits. The system is divided into different modules, including coin processing, product selection, dispensing mechanism, and change return logic. The design follows a structured approach, ensuring modularity and scalability.

#### 2. Finite State Machine (FSM) Development

FSM methodology is employed to manage the vending machine's operations efficiently. The system transitions through various states, including:

- Idle State: The machine waits for user input.

- Coin Acceptance State: The inserted coins are validated and stored.

- Selection State: The user selects a product, and the system verifies sufficient balance.

- **Dispensing State:** The selected item is dispensed.

- Change Return State: If required, the remaining balance is returned to the user.

This structured FSM approach ensures smooth operation and error handling.

#### 3. Synthesis and Implementation

The Verilog design is synthesized using Cadence Genus, optimizing for performance, power, and area (PPA). The implementation is further refined using Cadence Encounter, ensuring minimal area usage, efficient power consumption, and faster processing.

#### 4. Verification

To ensure correctness, a test bench is created for simulation. The test bench verifies different scenarios, including valid/invalid inputs, product availability, and balance handling, ensuring the FSM behaves as expected.

#### 5. Real-World Application

The final design is deployed on an FPGA board to demonstrate its feasibility in real-world applications. It interacts with physical components like buttons, displays, and actuators, validating real-time performance and making it suitable for commercial use.

#### 1.3 OVERVIEW OF THE PROJECT

The project "Design and Verification of Vending Machine Using Verilog HDL" focuses on the development of a digital vending machine using Finite State Machine (FSM) methodology. The vending machine transitions through multiple states, including idle, coin acceptance, validation, product dispensing, and change return. FSM-based design ensures structured state transitions, improving reliability and operational efficiency

#### Finite State Machine (FSM) Approach

FSM is a sequential circuit design method that ensures the vending machine correctly handles user inputs and system operations. The major states include:

- **Idle State:** The system remains in standby mode until a coin is inserted.

- Coin Acceptance State: The machine detects, verifies, and accumulates the inserted coins.

- Validation State: It checks if the inserted amount is sufficient for the selected product.

- **Product Selection and Dispensing State:** If the balance is adequate, the selected product is dispensed.

- Change Return State: Any remaining balance is returned to the user.

- Error Handling State: Manages invalid selections, insufficient funds, or incorrect inputs.

FSM ensures efficient state management and minimizes errors in user interactions.

#### Verilog HDL Implementation

The vending machine is designed using Verilog HDL, a hardware description language suitable for modeling digital circuits. The design is divided into modular components, including:

- Coin Processing Module: Registers and validates coin inputs.

- Product Selection Module: Detects and processes user selections.

- Control Logic Module: Implements FSM to control system operations.

- **Dispensing Mechanism Module:** Controls the release of selected products and change return.

This modular approach enhances design scalability, flexibility, and debugging efficiency. Verification through Testbench Simulation to ensure the design functions as expected, a testbench is created to simulate different operational scenarios:

- Valid and invalid coin insertions.

- Correct and incorrect product selections.

- Proper handling of insufficient balance.

- Ensuring correct change return and reset conditions.

Tools like Model Sim or Xilinx Vivado are used for functional verification.

Synthesis and FPGA Deployment. The Verilog code is synthesized using Cadence Genus, optimizing performance, power, and area (PPA). It is implemented using Cadence Encounter and tested on an FPGA board with real-time buttons, displays, and actuators for item dispensing.

### CHAPTER 2 LITERATURE SURVEY

#### 2.1. EXISTING SYSTEM

In modern vending machines, many designs employ microcontrollers or embedded systems for high-level control, often complemented by hardware description languages (HDLs) like Verilog to handle time-critical tasks. A widely adopted method for implementing vending machine logic involves using a Finite State Machine (FSM) architecture, typically implemented in Verilog, to manage the various operational states of the machine.

#### **Description of the Existing Method:**

The core of the vending machine operation is managed through a Finite State Machine (FSM), where each state represents a specific operation (e.g., idle, accepting coins, dispensing items, returning change). The FSM architecture is implemented using Verilog HDL to ensure efficient, fast, and reliable state transitions based on the user inputs, coin detection, and machine status.

In this existing method, the overall vending machine control is distributed between:

- A Microcontroller or Embedded Processor: Handles high-level tasks such as managing user interactions, interpreting inputs, and controlling the overall sequence of operations. The microcontroller might interface with a keypad or touchscreen for item selection and payment options.

- 2. **Verilog-based FSM**: Responsible for controlling hardware components like coin acceptance, item dispensing, and change return. The FSM ensures that the machine behaves predictably under different conditions, transitioning between various states based on user actions (inserting coins, selecting items, etc.).

- 3. Peripheral Devices and Control Logic: Verilog is also used to implement the control logic for peripherals like motors, solenoids, coin acceptors, and sensors. For example, the FSM in Verilog can trigger a motor to dispense an item or control the solenoid to return change.

#### **Disadvantages of the Existing Method:**

- 1. High Complexity in Hardware Design:

- Requires specialized knowledge of Verilog and digital logic design.

- Steep learning curve for engineers unfamiliar with hardware description languages.

#### 2. Long Design and Testing Cycles:

- Any changes to the FSM or hardware logic require full re-synthesis and re-testing.

- Time-consuming iteration and debugging process.

#### 3. Power Consumption:

- FPGA-based designs generally consume more power than microcontroller-based solutions.

- Higher power usage may increase operational costs, especially in large deployments.

#### 4. Difficulty in Handling Software-like Tasks:

- Verilog is not suitable for complex, high-level tasks like encryption, dynamic pricing, or mobile payment integration.

- May require additional microcontrollers or systems to handle non-time-critical operations.

#### 5. Hardware Dependency and Difficulty in Upgrades:

- Changes to the hardware or peripherals require significant changes to the Verilog code.

- Upgrades are not as flexible as software-based systems and may require reprogramming the FPGA.

#### 6. Difficulty in Scaling for More Complex Systems:

- As the system grows (e.g., more items, advanced payment options), the FSM becomes harder to manage.

- Scaling the design can lead to increased complexity and potential resource exhaustion.

# [1] Chopde, Abhay, et al. "Vending Machine Using Verilog (FPGA)." 2024 4th Asian Conference on Innovation in Technology (ASIANCON). IEEE, 2024.

The design and implementation of a vending machine system using Verilog HDL on an FPGA board. The vending machine is equipped with multiple states including product selection, amount selection, dispensing, out-of-stock detection, refund processing, change calculation, and system reset. The project aims to demonstrate the integration of hardware description language (Verilog) with FPGA technology to create a functional vending machine prototype. The design process involved the decomposition of the vending machine's functionality into smaller modules, each responsible for a specific task. These modules were then integrated to form the complete system.

# [2] Fuad, Mahamudul Hassan, et al. "Design of a Vending Machine Using Verilog HDL and Implementation in Genus & Encounter." *European Journal of Electrical Engineering and Computer Science* 7.6 (2023): 88-95.

This paper proposes the design, implementation, and verification of a vending machine using the Finite State Machine (FSM) methodology in Verilog HDL. The FSM is used to manage the multiple states of the vending machine, including "idle," "accepting coins," "dispensing item," and "returning change." The implementation of the vending machine is done in Verilog HDL, and the FSM is implemented as a state diagram. The design is then synthesized using the Genus synthesis tool and implemented using the Encounter implementation tool. The Genus tool uses advanced optimization techniques, such as timing-driven placement and clock tree synthesis, to improve the design's performance and area. The Encounter tool performs physical design, including placement and routing, to meet the design's timing, power, and area constraints. To validate the design's correctness and functionality, a test bench is created to simulate the behaviour of the vending machine. The simulation results are then used to verify that the design meets the required specifications and that the FSM behaves as expected. The proposed design is then can be implemented on a Field Programmable Gate Array (FPGA) to demonstrate its effectiveness in a real-world scenario. The results of the implementation are presented and analyzed to validate the design's performance, power consumption, and area. Overall, the vending machine using FSM in Verilog HDL, implemented in Genus and Encounter, provides a reliable and efficient solution for users to purchase items from the machine. The proposed design and implementation demonstrate the feasibility and effectiveness of this approach, and the results show that the design meets the required specifications and performs well in a real-world scenario.

# [3] Ravikumar, P., MV Ganeswara Rao, and Vamaraju Nikitha. "Verilog Based Automated Retail System." 2024 OPJU International Technology Conference (OTCON) on Smart Computing for Innovation and Advancement in Industry 4.0. IEEE, 2023.

The abstract describes an approach for implementing a vending machine using Verilog HDL. Verilog HDL is a hardware description language that can be used to model digital circuits. The proposed approach involves designing the vending machine using Verilog HDL and simulating the design to ensure it meets the required specifications. The design is then synthesized and implemented on a field-programmable gate array (FPGA). The vending machine is capable of accepting coins and dispensing products based on the user's selection.

#### 2.2 PROPOSED SYSTEM

An abstract machine that can only exist in one of the finite states at any one moment is called a finite state machine. It is a synchronous sequential machine described by an abstract model. A sequential machine's most basic model includes inputs, outputs, and internal states. A machine might have an endless number of alternative histories, therefore it would require an infinite capacity for storing them, since the output of a sequential circuit depends on both the current input and the previous inputs, or past histories. We only take into consideration finite state machines because it is not possible to create machines with limitless storage capacity.

Finite state machines are sequential circuits whose past histories can affect their future behaviour in only a finite number of ways, i.e., they are machines with a fixed number of states. These machines can distinguish among a finite number of classes of input histories. These classes of input histories are referred to as internal states of the machine. Every finite state machine therefore contains a finite number of memory devices. Problem Formulation: The design of a vending machine that dispenses three different priced products and takes coins with denominations of one, two, five and ten is the difficulty. The machine should also have the ability to return money upon request cancellation and change back when a coin of a higher denomination is input. The consumer is prompted by the machine to choose the product before inserting coins according to the product's price.

Therefore, the machine receives the select and coin signals as inputs. There is one more input, the cancel option. When the inserted quantity and the selected product's pricing match, the machine dispenses the product. The machine delivers the customer the product and the change if they insert a coin with a larger denomination. In the event that the machine does not have change, it returns the total. Thus, the machine's outputs are product and change. If a request is cancled, the money is repaid. Return money is thus an additional output. Two registers are required: one to record the number of coins in the current transaction and the other to record the overall number of coins in the machine. It is assumed that each register has ten bits of width. Change can only be provided when a higher denomination coin is inserted and the overall coin count exceeds the coin count of the current transaction. The machine determines if the change is available in this manner. These machines can distinguish among a finite number of classes of input histories.

These classes of input histories are referred to as internal states of the machine. Every finite state machine therefore contains a finite number of memory devices. Problem Formulation: The design of a vending machine that dispenses three different priced products and takes coins with denominations of one, two, five and ten is the difficulty. The machine should also have the ability to return money upon request cancellation and change back when a coin of a higher denomination is input. A machine might have an endless number of alternative histories, therefore it would require an infinite capacity for storing them, since the output of a sequential circuit depends on both the current input and the previous inputs, or past histories.

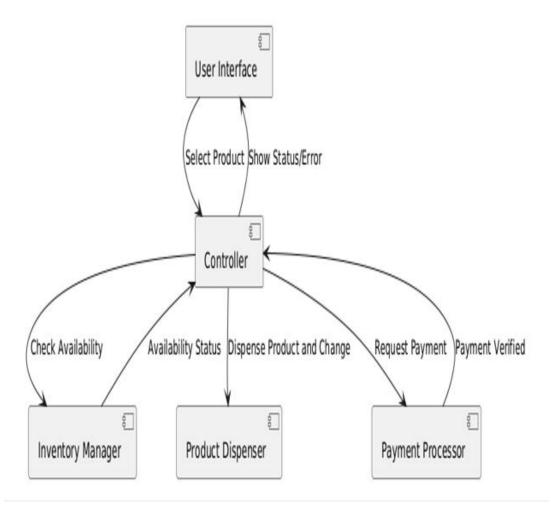

FIG 2.1: SIMPLIFIED VENDING MACHINE ARCHITECTURE

The functionality of a vending machine is controlled by an embedded system that processes user inputs, validates transactions, and dispenses selected items. These systems typically consist of multiple hardware and software components, including sensors, actuators, microcontrollers, and payment processing mechanisms.

Advanced vending machines integrate cashless payment options, such as credit/debit cards, mobile wallets, and QR code scanning, improving accessibility and user experience.

To ensure reliability and accuracy, vending machines employ digital logic circuits to handle various operations, such as coin detection, product selection, and change dispensing. The implementation of these digital circuits requires precise design methodologies that guarantee smooth transaction processing and error-free operation. This has led to the adoption of Hardware Description Languages (HDLs) such as Verilog for designing and implementing vending machine controllers. A machine might have an endless number of alternative histories, therefore it would require an infinite capacity.

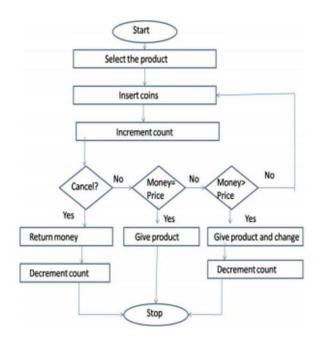

#### **Flow Chart:**

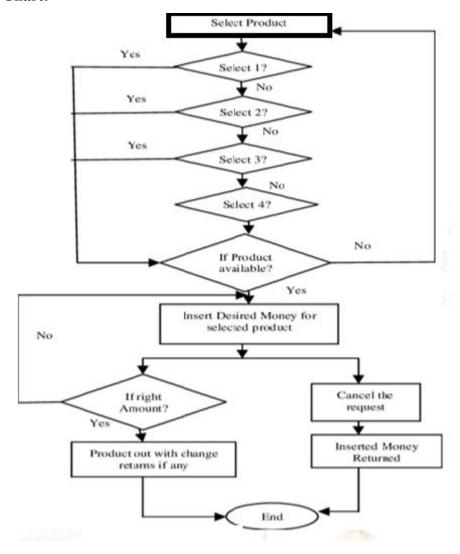

FIG 2.2: FLOW CHART

The product must be chosen first, and then the coins must be inserted. As coins are added, the count is increased. The machine decrements count and restores inserted money in the event that a cancel signal is delivered. If not, the device compares the amount of money entered with the cost of the chosen item. The machine dispenses the right product if both are equal. The machine will provide the right goods and change if the amount entered exceeds the pricing. The machine waits for the user to insert more coins if the amount of money inserted is less than the cost of the item they have chosen.

#### 2.3. INTRODUCTION TO VLSI

#### 2.3.1. VLSI TECHNOLOGY

VLSI Design presents state-of-the-art papers in VLSI design, computer-aided design, design analysis, design implementation, simulation and testing. Its scope also includes papers that address technical trends, pressing issues, and educational aspects in VLSI Design. The Journal provides a dynamic high-quality international forum for original papers and tutorials by academic, industrial, and other scholarly contributors in VLSI Design.

The development of microelectronics spans a time which is even lesser than the average life expectancy of a human, and yet it has seen as many as four generations. Early 60's saw the low density fabrication processes classified under Small Scale Integration (SSI) in which transistor count was limited to about 10. This rapidly gave way to Medium Scale Integration in the late 60's when around 100 transistors could be placed on a single chip. It was the time when the cost of research began to decline and private firms started entering the competition in contrast to the earlier years where the main burden was borne by the military. Transistor-Transistor logic (TTL) offering higher integration densities outlasted other IC families like ECL and became the basis of the first integrated circuit revolution. It was the production of this family that gave impetus to semiconductor giants like Texas Instruments, Fairchild and National Semiconductors. Early seventies marked the growth of transistor count to about 1000 per chip called the Large Scale Integration.

By mid-eighties, the transistor count on a single chip had already exceeded 1000 and hence came the age of Very Large Scale Integration or VLSI. Though many improvements have been made and the transistor count is still rising, further names of generations like ULSI are generally avoided. It was during this time when TTL lost the battle to MOS family owing

to the same problems that had pushed vacuum tubes into negligence, power dissipation and the limit it imposed on the number of gates that could be placed on a single die.

The second age of Integrated Circuits revolution started with the introduction of the first microprocessor, the 4004 by Intel in 1972 and the 8080 in 1974. Today many companies like Texas Instruments, Infineon, Alliance Semiconductors, Cadence, Synopsys, Celox Networks, Cisco, Micron Tech, National Semiconductors, ST Microelectronics, Qualcomm, Lucent, Mentor Graphics, Analog Devices, Intel, Philips, Motorola and many other firms have been established and are dedicated to the various fields in "VLSI" like Programmable Logic Devices, Hardware Descriptive Languages, Design tools, Embedded Systems etc. In 1980s, hold-over from outdated taxonomy for integration levels. Obviously, influenced

In 1980s, hold-over from outdated taxonomy for integration levels. Obviously, influenced from frequency bands, i.e., HF, VHF, and UHF. Sources disagree on what is measured (gates or transistors)

SSI – Small-Scale Integration (0-102)

MSI – Medium-Scale Integration (102 -103)

LSI – Large-Scale Integration (103 -105)

VLSI – Very Large-Scale Integration (105 - 107)

ULSI – Ultra Large-Scale Integration (>= 107)

The company was based in Silicon Valley, with headquarters at 1109 McKay Drive in San Jose, California. Along with LSI Logic, VLSI Technology defined the leading edge of the application-specific integrated circuit (ASIC) business, which accelerated the push of powerful embedded systems into affordable products. The company was founded in 1979 by a trio from Fairchild Semiconductor by way of Synertek - Jack Balletto, Dan Floyd, and Gunnar Wetlesen - and by Doug Fairbairn of Xerox PARC and Lambda (later VLSI Design) magazine. Alfred J. Stein became the CEO of the company in 1982. Subsequently VLSI built its first fab in San Jose; eventually a second fab was built in San Antonio, Texas. VLSI had its initial public offering in 1983, and was listed on the stock market as (NASDAQ: VLSI). The company was later acquired by Philips and survives to this day as part of NXP Semiconductors.

The first semiconductor chips held two transistors each. Subsequent advances added more and more transistors, and, as a consequence, more individual functions or systems were integrated over time. The first integrated circuits held Only a few devices, perhaps as many as ten diodes, transistors, resistors and capacitors, making it possible to fabricate one or more logic gates on a single device.

Now, known retrospectively as small-scale integration (SSI), improvements in technique led to devices with hundreds of logic gates, known as medium-scale integration (MSI). Further improvements led to large-scale integration (LSI), i.e. systems with at least a thousand logic gates.

At one time, there was an effort to name and calibrate various levels of large-scale integration above VLSI. Terms like ultra-large-scale integration (ULSI) were used. But the huge number of gates and transistors available on common. Current designs, as opposed to the earliest devices, use extensive design automation and automated logic synthesis to lay out the transistors, enabling higher levels of complexity in the resulting logic functionality. Certain high-performance logic blocks like the SRAM (Static Random Access Memory) cell, however, are still designed by hand to ensure the highest efficiency (sometimes by bending or breaking established design rules to obtain the last bit of performance by trading stability) [citation needed]. VLSI technology is moving towards radical level miniaturization with introduction of NEMS technology. A lot of problems need to be sorted out before the transition is actually made.

#### **2.3.2. WHY VLSI?**

Integration improves the design, lowers the parasitics, which means higher speed and lower power consumption and physically smaller. The Integration reduces manufacturing cost - (almost) no manual assembly.

The course will cover basic theory and techniques of digital VLSI design in CMOS technology. Topics include: CMOS devices and circuits, fabrication processes, static and dynamic logic structures, chip layout, simulation and testing, low power techniques, design tools and methodologies.

There is an emphasis on modern design issues in interconnect and clocking. We will also use several case-studies to explore recent real-world VLSI designs (e.g. Pentium, Alpha, PowerPC Strong ARM, etc.) and papers from the recent research literature. On-campus students will design small test circuits using various CAD tools. Circuits will be verified and analyzed for performance with various simulators. Some final project designs will be fabricated and returned to students the following semester for testing.

Very-large-scale integration (VLSI) is the process of creating integrated circuits by combining thousands of transistor-based circuits into a single chip. VLSI began in the 1970s when complex semiconductor and communication technologies were being developed. The microprocessor is a VLSI device. The term is no longer as common as it once was, as chips have increased in complexity into the hundreds of millions of transistors. The first semiconductor chips held one transistor each.

Subsequent advances added more and more transistors, and, as a consequence, more individual functions or systems were integrated over time. The first integrated circuits held only a few devices, perhaps as many as ten diodes, transistors, resistors and capacitors, making it possible to fabricate one or more logic gates on a single device. Further improvements led to large-scale integration (LSI), i.e. systems with at least a thousand logic gates. Current technology has moved far past this mark and today's microprocessors have many millions of gates and billions of individual transistors.

Now known retrospectively as "small-scale integration" (SSI), improvements in technique led to devices with hundreds of logic gates, known as large-scale integration (LSI), i.e. systems with at least a thousand logic gates. Current technology has moved far past this mark and today's microprocessors have many millions of gates and hundreds of millions of individual transistors.

At one time, there was an effort to name and calibrate various levels of large-scale integration above VLSI. Terms like Ultra-large-scale Integration (ULSI) were used. But the huge number of gates and transistors available on common devices has rendered such fine distinctions moot. Terms suggesting greater than VLSI levels of integration are no longer in widespread use. Even VLSI is now somewhat quaint, given the common assumption that all microprocessors are VLSI or better.

This microprocessor is unique in the fact that its 1.4 Billion transistor count, capable of a teraflop of performance, is almost entirely dedicated to logic (Itanium's transistor count is largely due to the 24MB L3 cache). Current designs, as opposed to the earliest devices, use extensive design automation and automated logic synthesis to lay out the transistors, enabling higher levels of complexity in the resulting logic functionality. Certain high-performance logic blocks like the SRAM cell, however, are still designed by hand to ensure the highest efficiency (sometimes by bending or breaking established design rules to obtain the last bit of performance by trading stability).

The original business plan was to be a contract wafer fabrication company, but the venture investors wanted the company to develop IC (Integrated Circuit) design tools to help fill the foundry. Thanks to its Caltech and UC Berkeley students, VLSI was an important pioneer in the electronic design automation industry. It offered a sophisticated package of tools, originally based on the 'lambda-based' design style advocated by Carver Mead and Lynn Conway.

VLSI became an early vendor of standard cell (cell-based technology) to the merchant market in the early 80s where the other ASIC-focused company, LSI Logic, was a leader in gate arrays. Prior to VLSI's cell-based offering, the technology had been primarily available only within large vertically integrated companies with semiconductor units such as AT&T and IBM. VLSI's design tools eventually included not only design entry and simulation but eventually cell-based routing (chip compiler), a data path compiler, SRAM and ROM compilers and a state machine compiler. The tools were an integrated design solution for IC design and not just point tools, or more general purpose system tools.

A designer could edit transistor-level polygons and/or logic schematics, then run DRC and LVS, extract parasites from the layout and run Spice simulation, then back-annotate the timing or gate size changes into the logic schematic database. Characterization tools were integrated to generate Frame Maker Data Sheets for Libraries. VLSI eventually spun off the CAD and Library operation into Compass Design Automation but it never reached IPO before it was purchased by Avanti Corp.

VLSI's physical design tools were critical not only to its ASIC business, but also in setting the bar for the commercial EDA industry. When VLSI and its main ASIC competitor, LSI Logic, were establishing the ASIC industry, commercially-available tools could not deliver the productivity necessary to support the physical design of hundreds of ASIC designs each year without the deployment of a substantial number of layout engineers. The companies' development of automated layout tools was a rational "make because there's nothing to buy" decision. The EDA industry finally caught up in the late 1980s when Tangent Systems released its Tan Cell and Tan Gate products. In 1989, Tangent was acquired by Cadence Design Systems (founded in 1988).

Unfortunately, for all VLSI's initial competence in design tools, they were not leaders in semiconductor manufacturing technology. VLSI had not been timely in developing a 1.0 µm manufacturing process as the rest of the industry moved to that geometry in the late 80s. VLSI entered a long-term technology partnership with Hitachi and finally released a 1.0 µm process and cell library (actually more of a 1.2 µm library with a 1.0 µm gate). As VLSI struggled to gain parity with the rest of the industry in semiconductor technology, the design flow was moving rapidly to a Verilog HDL and synthesis flow. Cadence acquired Gateway, the leader in Verilog hardware design language (HDL) and Synopsys was dominating the exploding field of design synthesis.

Meanwhile, VLSI entered the merchant high speed static RAM (SRAM) market as they needed a product to drive the semiconductor process technology development. All the large semiconductor companies built high speed SRAMs with cost structures VLSI could never match. ARM Ltd was formed in 1990 as a semiconductor intellectual property licensor, backed by Acorn, Apple and VLSI. VLSI became a licensee of the powerful ARM processor and ARM finally funded processor tools. Initial adoption of the ARM processor was slow. Few applications could justify the overhead of an embedded 32 bit processor. Only in PC chipsets, did VLSI dominate in the early 90s. This product was developed by five engineers using the 'Mega cells" in the VLSI library that led to a business unit at VLSI that almost equaled its ASIC business in revenue. VLSI eventually ceded the market to Intel because Intel was able to package-sell its processors, chipsets, and even board level products together.

VLSI also had an early partnership with PMC, a design group that had been nurtured of British Columbia Bell. When PMC wanted to divest its semiconductor intellectual property venture, VLSI's bid was beaten by a creative deal by Sierra Semiconductor. The telecom business unit management at VLSI opted to go it alone. PMC Sierra became one of the most important telecom ASSP vendors. Scientists and innovations from the 'design technology' part of VLSI found their way to Cadence Design Systems (by way of Redwood Design Automation). Compass Design Automation (VLSI's CAD and Library spin-off) was sold to Avant! Corporation, which itself was acquired by Synopsys.

#### 2.3.3. Structured design

Structured VLSI design is a modular methodology originated by Carver Mead and Lynn Conway for saving microchip area by minimizing the interconnect fabrics area.

This is obtained by repetitive arrangement of rectangular macro blocks which can be interconnected using wiring by abutment. An example is partitioning the layout of an adder into a row of equal bit slices cells. In complex designs this structuring may be achieved by hierarchical nesting.

Structured VLSI design had been popular in the early 1980s, but lost its popularity later because of the advent of placement and routing tools wasting a lot of area by routing, which is tolerated because of the progress of Moore's Law. When introducing the hardware description language KARL in the mid' 1970s, Reiner Hartenstein coined the term "structured VLSI design" echoing Edsger Dijkstra's structured programming approach by procedure nesting to avoid chaotic spaghetti-structured program.

Only in PC chipsets, did VLSI dominate in the early 90s. This product was developed by five engineers using the 'Mega cells" in the VLSI library that led to a business unit at VLSI that almost equaled its ASIC business in revenue. semiconductor technology, the design flow was moving rapidly to a Verilog HDL and synthesis flow. Cadence acquired Gateway, the leader in Verilog hardware design language (HDL) and Synopsys was dominating the exploding field of design synthesis.

#### 2.3.4. APPLICATIONS OF VLSI

- Electronic system in cars.

- Digital electronics control VCRs

- > Transaction processing system, ATM

- Personal computers and Workstations

Electronic systems now perform a wide variety of tasks in daily life. Electronic systems in some cases have replaced mechanisms that operated mechanically, hydraulically, or by other means; electronics are usually smaller, more flexible, and easier to service. In other cases electronic systems have created totally new applications. Electronic systems perform a variety of tasks; some of them are visible while some are hidden.

Personal entertainment systems such as portable MP3 players and DVD players perform sophisticated algorithms with remarkably little energy. Electronic systems in cars operate stereo systems and displays; they also control fuel injection systems, adjust suspensions to varying terrain, and perform the control functions required for anti-lock braking systems.

Digital electronics compress and decompress video, even at high-definition data rates, onthe-fly in consumer electronics. Low-cost terminals for Web browsing still require sophisticated electronics, despite their dedicated function. Personal computers and workstations provide word-processing, financial analysis, and games. Computers include both central processing units and special-purpose hardware for disk access, faster screen display, etc.

Medical electronic systems measure bodily functions and perform complex processing algorithms to warn about unusual conditions. The availability of these complex systems, far from overwhelming consumers. The growing sophistication of applications continually pushes the design and manufacturing of integrated circuits and electronic systems to new levels of complexity. And perhaps the most amazing characteristic of this collection of systems is its variety-as systems become more complex, we build not a few general-purpose computers but an eve wider range of special-purpose systems.

Our ability to do so is a testament to our growing mastery of both integrated circuit manufacturing and design, but the increasing demands of customers continue to test the limits of design and manufacturing. Electronic systems in cars operate stereo systems and displays; they also control fuel injection systems, adjust suspensions to varying terrain, and perform the control functions required for anti-lock braking systems.

#### 2.3.5. **ASIC**

An Application-Specific Integrated Circuit (ASIC) is an integrated circuit (IC) customized for a particular use, rather than intended for general-purpose use. For example, a chip designed solely to run a cell phone is an ASIC. Intermediate between ASICs and industry standard integrated circuits, like the 7400 or the 4000 series, are application specific standard products (ASSPs).

As feature sizes have shrunk and design tools improved over the years, the maximum complexity (and hence functionality) possible in an ASIC has grown from 5,000 gates to over 100 million. Modern ASICs often include entire 32-bit processors, memory blocks including ROM, RAM, EEPROM, Flash and other large building blocks. Such an ASIC is often termed a SoC (system-on-a-chip). Designers of digital ASICs use a hardware description language (HDL), such as Verilog or VHDL, to describe the functionality of ASICs. Field-programmable gate arrays (FPGA).

The modern-day technology for building a breadboard or prototype from standard parts; programmable logic blocks and programmable interconnects allow the same FPGA to be used in many different applications. For smaller designs and/or lower production volumes, FPGAs may be more cost effective than an ASIC design even in production.

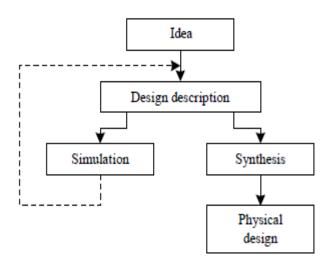

#### 2.3.6. ASIC DESIGN FLOW

As with any other technical activity, development of an ASIC starts with an idea and takes tangible shape through the stages of development. The first step in this process is to expand the idea in terms of behaviour of the target circuit. The growing sophistication of applications continually pushes the design and manufacturing of integrated circuits and electronic systems to new levels of complexity.

Design description is an activity independent of the target technology or manufacturer. It results in a description of the digital circuit. To translate it into a tangible circuit, one goes through the physical design process. The same constitutes a set of activities closely linked to the manufacturer and the target technology.

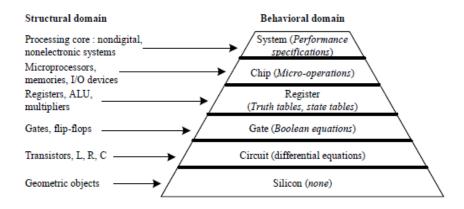

FIG 2.3: ASIC DESIGN

The design is tested through a simulation process; it is to check, verify, and ensure that what is wanted is what is described. Simulation is carried out through dedicated tools. With every simulation run, the simulation results are studied to identify errors in the design description. The errors are corrected and another simulation run carried out.

FIG 2.4: ASIC DESIGN FLOW

#### **CHAPTER 3**

#### **SOFTWARE REQUIREMENTS**

#### 3.1 XILINX ISE

Xilinx, Inc. is the world's largest provider of programmable common sense devices, the inventor of the field programmable gate array (FPGA) and the primary semiconductor organization with a fabless manufacturing version. Xilinx designs, develops and markets programmable logic merchandise including incorporated circuits (ICs), software program design equipment and predefined gadget functions added as intellectual property (IP) cores, design offerings, patron education, area engineering and technical assist. Xilinx sells each FPGAs and CPLDs programmable common sense devices for electronic equipment producers in cease markets along with communications, commercial, customer, automobile and statistics processing.

Xilinx's FPGAs have even been used for the ALICE (A huge Ion Collider test) on the CERN ecu laboratory at the French-Swiss border to map and disentangle the trajectories of heaps of subatomic debris. The Vertex-II seasoned, Virtex-6, Virtex-five, and Virtex-6 FPGA families are mainly focused on gadget-on-chip (SOC) designers due to the fact they consist of up to two embedded IBM PowerPC cores. The ISE layout Suite is the critical digital design automation (EDA) product own family sold by using Xilinx.

The ISE design Suite features include design access and synthesis assisting Verilog or VHDL, place-and-route (PAR), completed verification and debug using Chip Scope pro equipment, and advent of the bit documents which can be used to configure the chip. XST-Xilinx Synthesis era performs device particular synthesis for Cool Runner XPLA3/-II and XC9600/XL/XV households and generates an NGC report ready for the CPLD more fit.

#### **3.2 XILINX ISE 13.2i:**

Xilinx is the maximum important tool and in this device we are able to carry out both simulation and synthesis.

#### 3.2.1 Simulation:

In this process, we are going to verify our required output to get the simulation technique first of all we need to enforce a top module (combination of all modules) after which in the simulation conduct we can simulate the result.

#### 3.2.2 Synthesis:

Synthesis process defines converting Verilog code into gate level which creates a net list.

#### 3.2.3 Procedure:

- Click project navigator

- Create new project

- Selection of FPGA

#### Create new source

- Select source type (Verilog module)

- Coding

- Declaration of inputs and output

- Sources for implementation

#### Synthesize – XST

- Check syntax

- View design summary

- View RTL schematic

- View technology schematic

- Sources for behavioural simulation

#### Create new source

- Select source type (Verilog text fixture)

- Write test bench code

- Xilinx ISE simulator

- Behavioural check syntax

- Simulate behavioural model

#### **3.3 PROCEDURE FOR SYNTHESIS:**

Xilinx designs, develops and markets programmable logic merchandise including incorporated circuits (ICs), software program design equipment and predefined gadget functions added as intellectual property (IP) cores, design offerings, patron education, area engineering and technical assist. Xilinx sells each FPGAs and CPLDs programmable common sense devices for electronic equipment producers in cease markets along with communications, commercial, customer, automobile and statistics processing.

It is a comprehensive software suite that offers a modern platform for the design, synthesis, and verification of FPGA-based systems.

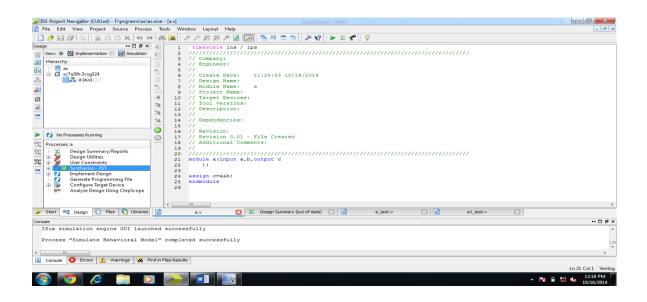

#### PROCEDURE FOR XILINX

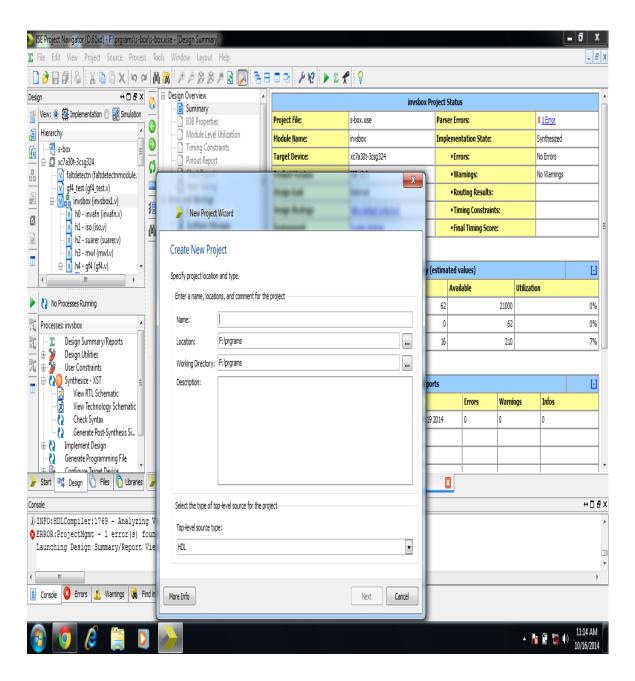

1.To create new project in xilinx we should open the filemenu, click on new project then it will open the dialogbox as below in that typethe filename click on next

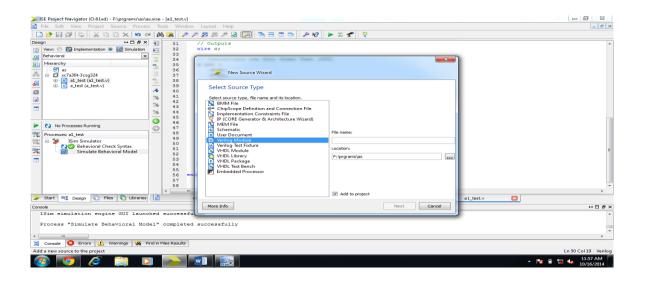

FIG 3.1: CREATING NEW FILE IN XILINX

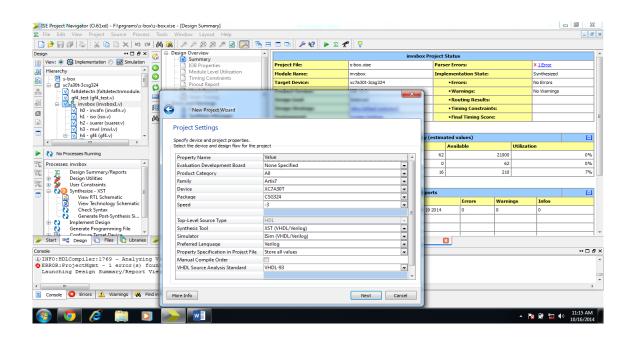

2. Then it isplays one more dialogbox which will give us the specifications of the project, click on next

FIG 3.2: DISPLAYS ONE MORE DAILOG BOX FOR SPECIFICATIONS IN XILINX

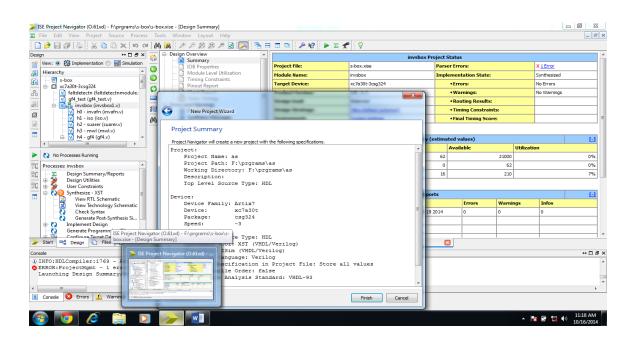

3. Then it again displays a dialogue box as shown below with the created project description and click finish to compelte the process of creating new project

FIG 3.3: DISPLAYS AGAIN A DAILOG BOX AS SHOWN BELOW WITH THE CREATED PROJECT DESCRIPTION IN XILINX

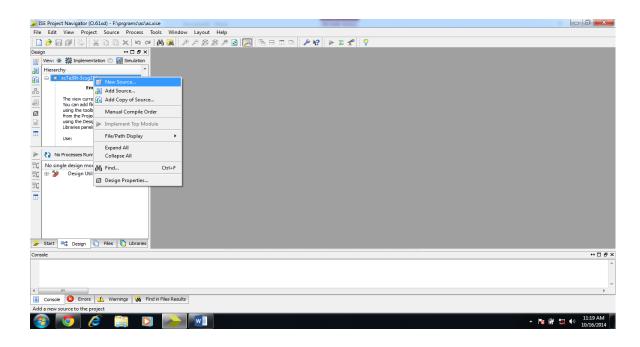

4. Now project with specifyed name is created then create the verilog files in the project. To create filesr, right click on the project that will show options like as shown below

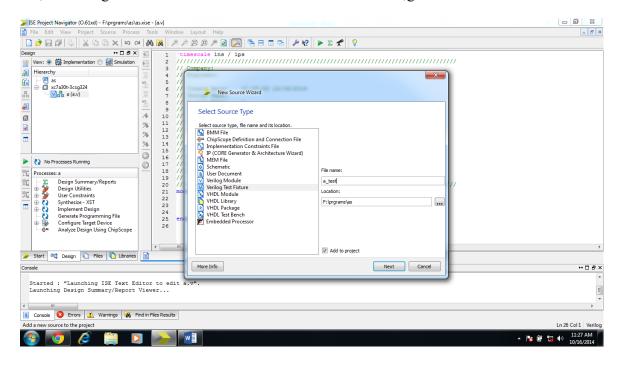

FIG 3.4: SPECIFIED NAME IS CREATED THEN CREATE THE VERILOG FILES IN THE PROJECT

5.From the given options select new source then it diaplays dialogbox which is containing of list of fileformat now we want to create verlogfile so select veilog module, and give the name to the file. Then click on next

FIG 3.5: SELECT NEW SOURCE THE IT DISPLAYS DAILOGBOX WHICH IS CONTAINING OF LIST OF FILE FORMAT IN XILINX

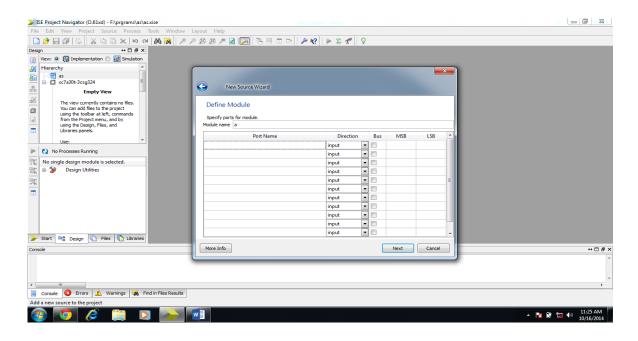

6. Then it will ask us to select inputs, outputs and inouts. We can specify our inputs and outputs here else we may also specify as part of programme depend upon the user requirement, click on next

FIG 3.6: SELECT INPUTS & OUTPUTS AND INOUTS IN XILINX

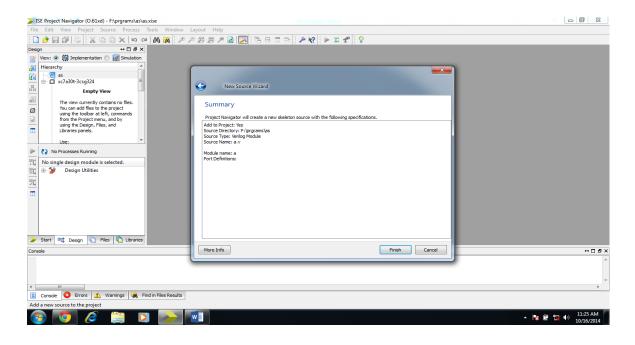

7. It will again displays a dilagbox by fiving details of filename etc, click on next

FIG 3.7: DISPLAYS AGAIN A DAILOGBOX BY FIVING DETAILS OF FILENAME IN XILINX

8.It will open a white space in the project window containing filename the double click on the file name so that it will displays respective file windows, where we should write the code

FIG 3.8: OPEN A WHITE SPACE IN THE PROJECT WINDOW CONTAINING FILENAME IN XILINX

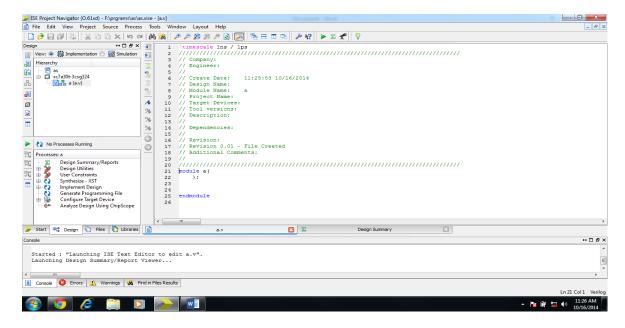

9. After completion writing code select the file name and click on synthesis which will check for errors, if there are any errors in syntax or design errors are checked and shown in the below of file window

FIG 3.9: WRITING CODE SELECT THE FILENAME IN XILINX

10.After sucessful synthesis we should have to create tesh bench file with extension as test, for that again riht click on the file name as shown below, give filename

FIG 3.10: AFTER SUCCESSFUL SYNTHESIS WE SHOULD HAVE TO CREATE TEST BENCH FILE IN XILINX

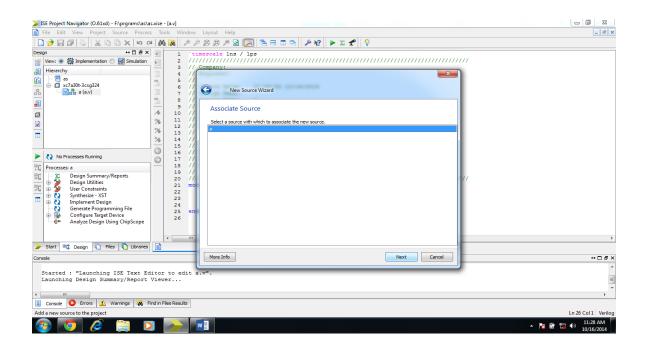

11. If there are list files then select file for which we are creating the test bench. Click on next

FIG 3.11: LIST FILES THEN SELECT FILE FOR WHICH WE ARE CREATING THE TEST BENCH IN XILINX

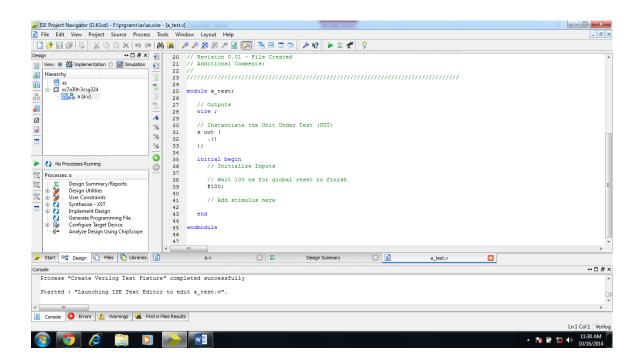

12.It again gives a testbench file in the project window, then give reqired inputs

FIG 3.12: GIVE A TEST BENCH FILE IN THE PROJECT WINDOW IN XILINX

13.select simulation from the view bar in the project window above the hiearchy window as follows.

FIG 3.13: SELECT SIMULATION FROM THE VIEW BAR IN THE PROJECT WINDOW IN XILINX

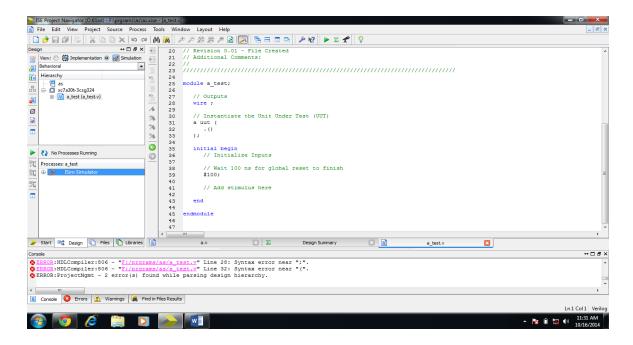

14. Double click on Isim Simulator it will expand as follows click on behavioural check syntax and it will check for syntax errors in test bench file

FIG 3.14: DOUBLE CLICK ON ISE SIMULATOR IN XILINX

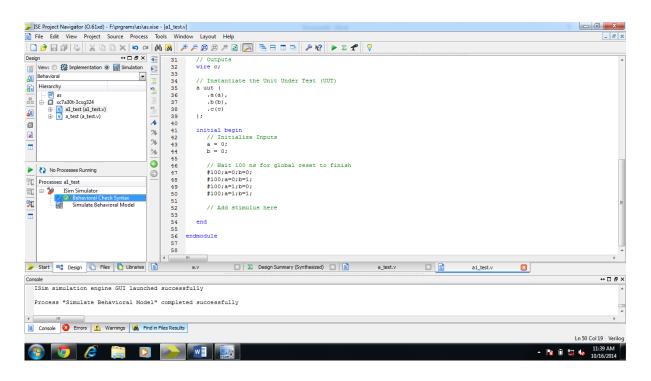

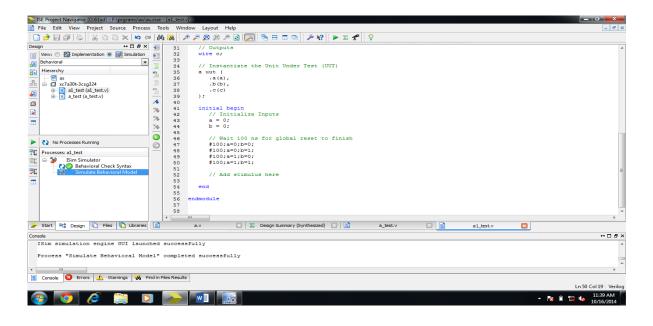

15. click on simulate behavioural model, it will displays wave form for in response to the inputs given in the test bench file

FIG 3.15: CLICK ON SIMULATE BEHAVIOURAL MODEL IN XILINX

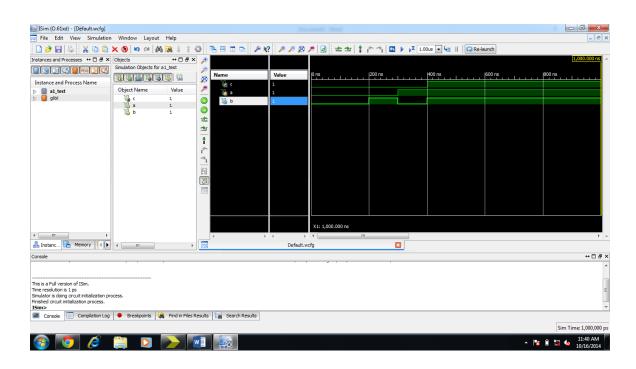

16. That wave form window having option to zoom out, zoom in to analyze the wave form clearly in order to understand behaviour of design

FIG 3.16: WAVEFORM WINDOW HAVING OPTION TO ZOOMOUT & ZOOM IN, IN XILINX

### VIVADO SOFTWARE

Here we have used XILINX updated version that is VIVADO SOFTWARE TOOL

Vivado is Xilinx's flagship design suite for FPGA and System-on-Chip (SoC) development. It is a comprehensive software suite that offers a modern platform for the design, synthesis, and verification of FPGA-based systems. Vivado replaces the older ISE Design Suite and provides a more advanced and integrated environment for high-performance FPGA development.

### **Key Features of Vivado:**

- 1. **High-Level Synthesis (HLS):** Vivado allows users to design systems using C, C++, and System C code, which is then automatically converted into hardware description language (HDL) code for FPGA implementation. This feature speeds up the design process and makes it easier to implement complex algorithms.

- 2. **IP Integrator:** Vivado includes a powerful IP catalog that provides pre-designed modules (IP cores) that can be integrated into a design. These IP cores cover a wide range of functionality, including communication protocols, memory controllers, and more.

- 3. **Synthesis and Implementation:** Vivado provides powerful tools for synthesizing and optimizing designs. It uses advanced place and route algorithms to ensure efficient use of FPGA resources, maximizing performance, minimizing power consumption, and reducing area.

- 4. **Simulation and Debugging:** Vivado includes built-in simulation tools like Vivado Simulator and support for Model Sim, making it easier to test and debug your design. Debugging tools like Integrated Logic Analyzer (ILA) and Chip Scope help you capture internal signals and verify functionality in real-time on the FPGA hardware.

- 5. **Constraint Management:** Vivado allows you to define timing, placement, and resource constraints, ensuring your design meets performance goals and works within the limitations of the target FPGA.

- 6. **Programming and Deployment:** Vivado allows direct FPGA programming through the software, helping

- 7. load the final bitstream file onto the FPGA board.

- 8. VIVADO is made with a superior synergistic blend of natural extracts and vitamins to provide complete immunity and cardio coverage.

### **How Vivado is Used in FPGA Development:**

- 1. **Design Creation:** You can create your digital design in Vivado using either HDL (Verilog or VHDL) or high-level synthesis tools (C, C++).

- 2. **Synthesis:** After writing your HDL code, Vivado synthesizes the design, turning your HDL code into a netlist that describes how the hardware will be implemented on the FPGA.

- 3. **Implementation:** The implementation step involves mapping the synthesized netlist onto the FPGA hardware, considering factors like placement (where elements are physically located on the FPGA) and routing (how signals are connected between elements).

- 4. **Simulation:** Vivado supports both pre-synthesis and post-synthesis simulation to ensure that your design functions correctly before it's deployed onto the actual FPGA.

- 5. **Optimization:** Vivado helps optimize the design for performance (speed), power, and area by adjusting the synthesized netlist and applying specific place and route optimizations.

- 6. **Bitstream Generation:** Once the design is verified, Vivado generates a bitstream file that configures the FPGA with your design. This file is then downloaded onto the FPGA for real-time operation.

- 7. **Debugging and Verification:** Vivado supports real-time debugging by connecting the FPGA to the Vivado Logic Analyzer or Chip Scope, enabling you to capture and analyze internal signals during execution, ensuring your design works as expected.

### **How Vivado Works:**

Vivado simplifies the process of designing, synthesizing, verifying, and deploying FPGA systems. After creating the design (in Verilog, VHDL, or C/C++), Vivado compiles the code into a configuration file (bitstream), which is uploaded to the FPGA hardware. The FPGA then implements the logic and functionality specified in the design, interacting with external peripherals, sensors, or other devices. Vivado Design Suite, developed by AMD (formerly Xilinx), is a comprehensive software environment for the synthesis and analysis of hardware description language (HDL) designs. It's crucial for designing and implementing complex digital circuits on Field-Programmable Gate Arrays (FPGAs) and Adaptive SoCs.

### STEPS FOR VIVADO SOFTWARE

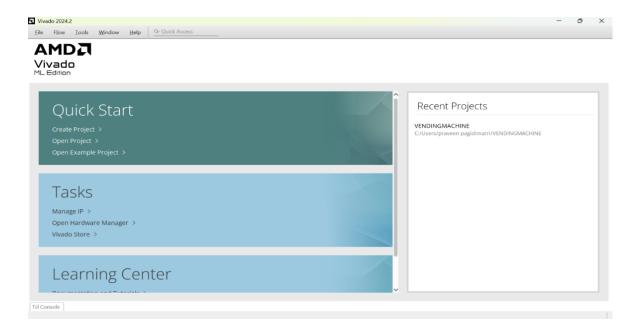

**STEP1:** Interface of the vivado software

FIG 3.17: INTERFACE OF THE VIVADO SOFTWARE

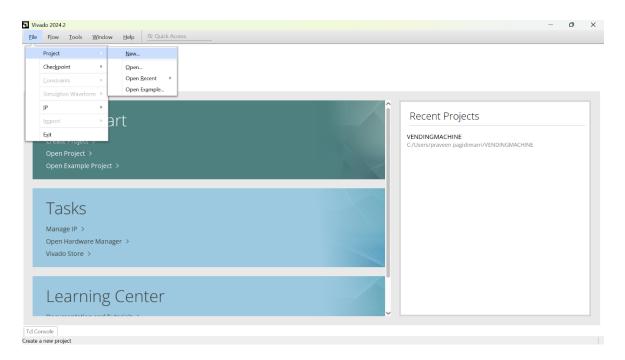

# STEP2: To create a project go to the file and click on project then click on new

FIG 3.18: TO CREATE A PROJECT GO TO THE FILE AND CLICK ON PROJECT

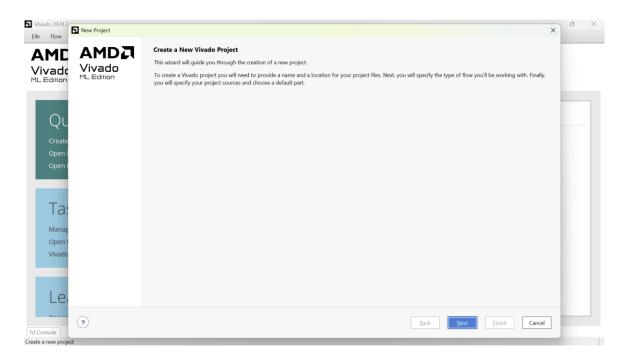

### **STEP3:** Click on next

FIG 3.18: CREATE A NEW VIVADO PROJECT

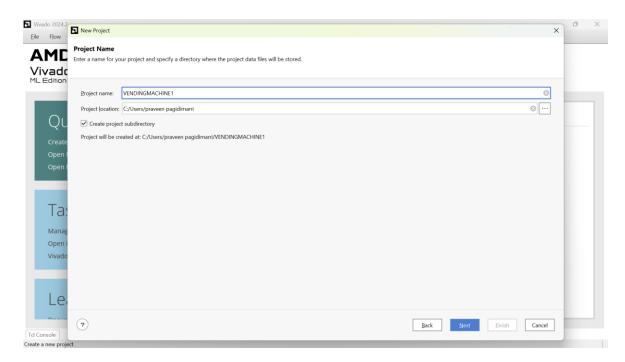

# STEP4: Give project name without space then click next

FIG 3.19: CREATE PROJECT NAME

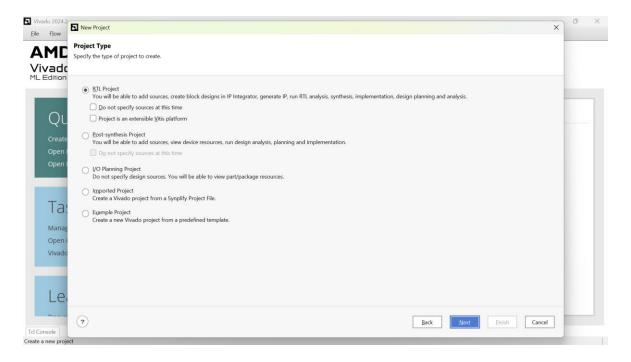

# STEP5: Select RTL Project then click next

FIG 3.20: SELECTING PROJECT TYPE

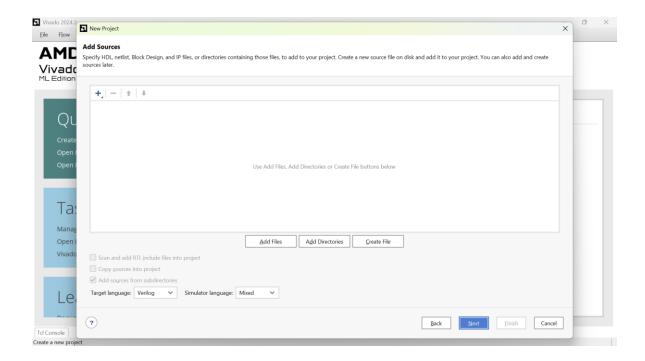

### STEP6: Select add files

FIG 3.21: ADDING FILES VIVADO

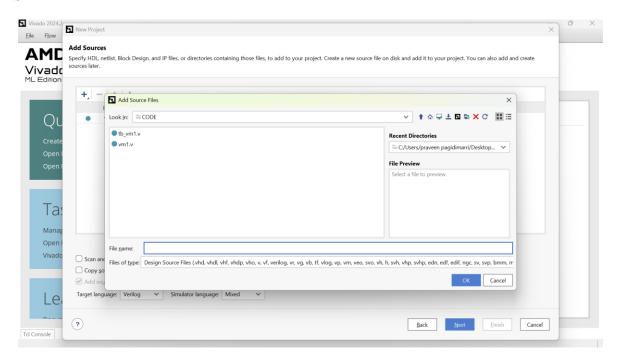

STEP7: Then it shows some file select the code click on ok

FIG 3.22: SELECTING CODE IN VAVADO

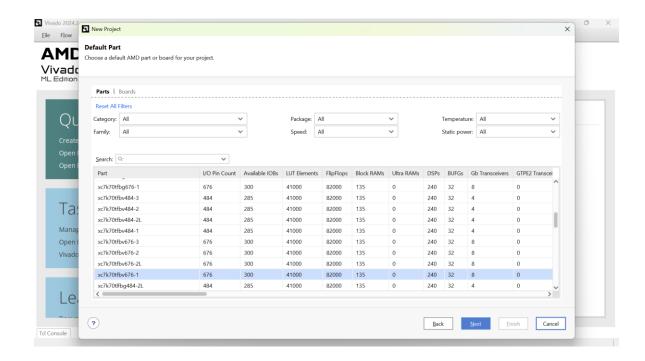

### STEP8: Click on next

FIG 3.23: SELECTING THE DEFAULT PART

### STEP9: Click on finish

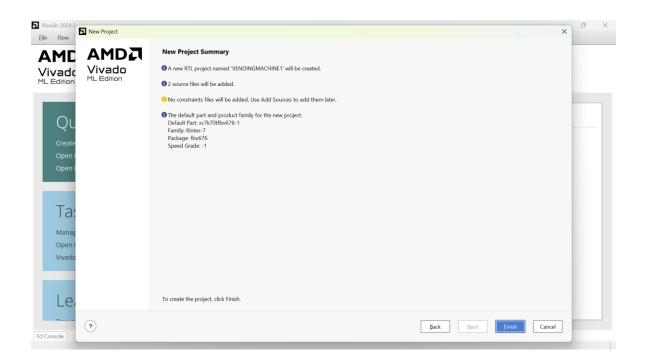

FIG 3.24: SELECTING THE FINAL STEP OF PROJECT CREATING

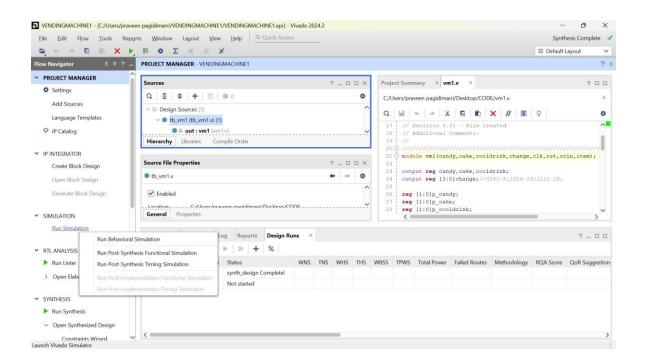

## STEP10: It is the project manager

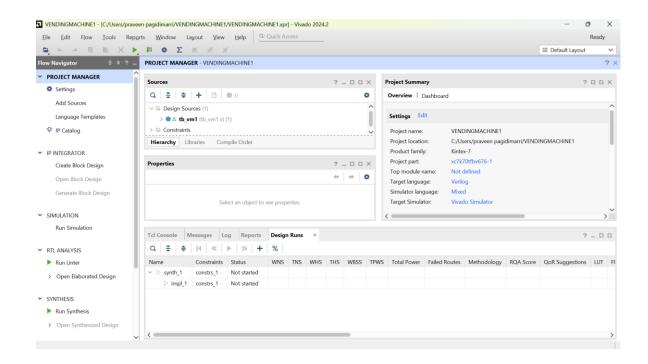

FIG 3.25: PROJECT MANAGER OF VIVADO SOFTWERE

## **STEP11:** On left side is project summary

FIG 3.26: PROJECT SUMMARY OF VIVADO SOFTWARE

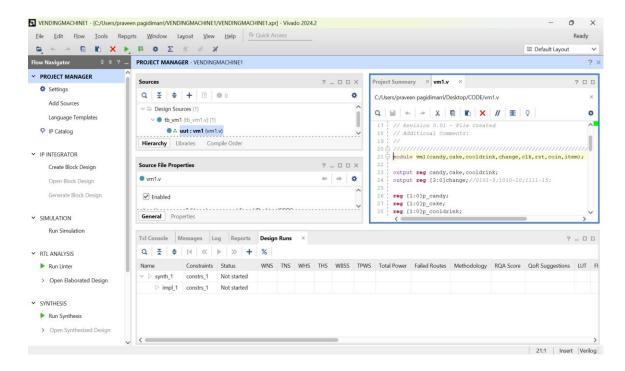

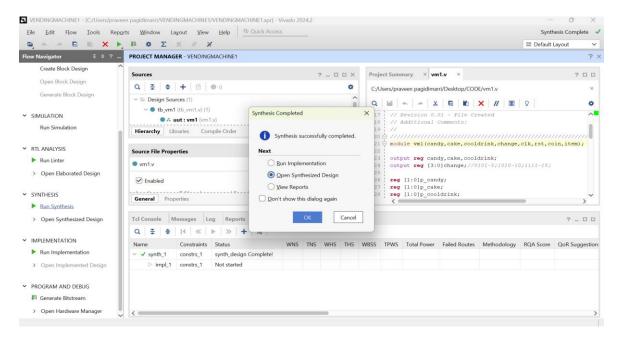

### STEP12: In design source click on uut: vm1 then click Run Synthesis

FIG 3.27: IN DESIGNING SOURCE SELECTING RUN SYNTHESIS

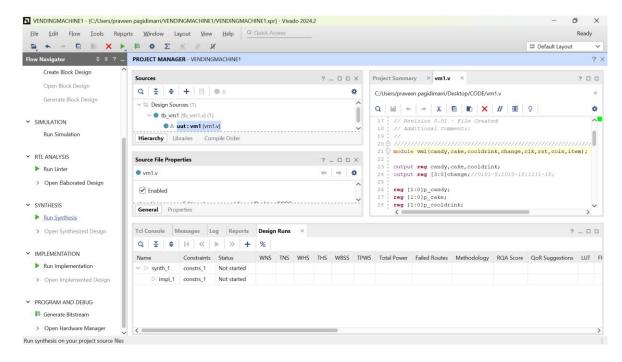

## STEP13: Select open synthesized design click ok

FIG 3.28: OPEN SYNTHESIZED DESIGN CLICK OK

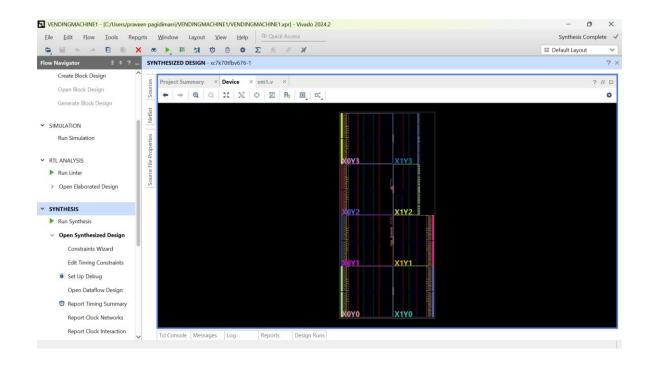

## STEP14: Synthesized design

FIG 3.29: SYNTHESIZED DESIGN

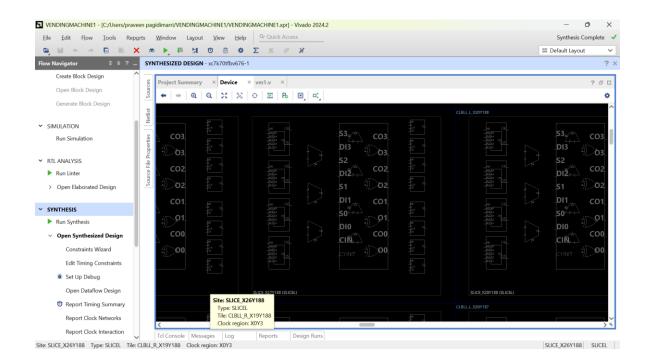

## STEP15: Inside synthesized design

FIG 3.30: INSIDE SYNTHESIZED DESIGN

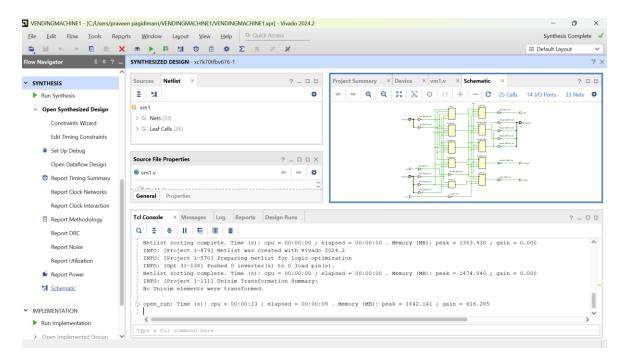

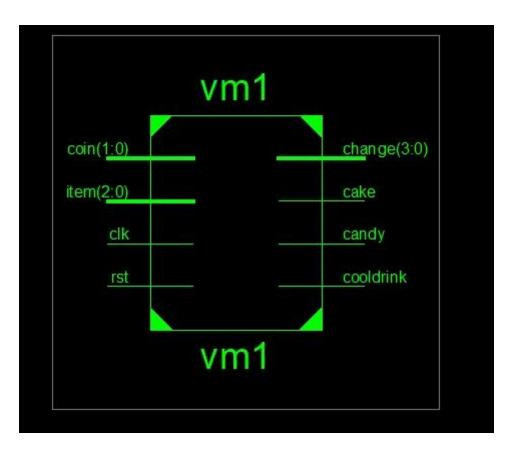

STEP16: Clicking on schematic in project summary schematic diagram

FIG 3.31: SELECTING ON SCHEMATIC IN PROJECT SUMMARY

**STEP 17:** In design source click on tb\_vm1 then Run Simulation select Run Behavioural Simulation

FIG 3.32: RUN SIMULATION AND SELECT BEHAVIOURAL SIMULATION

### **STEP18:** It is simulation

FIG 3.33: FINAL PART IN VIVADO SIMULATION PART

## **CHAPTER 4**

## WORKING OF THE PROJECT

## 4.1 WORKING OF THE PROJECT

### **BLOCK DIAGRAM**

FIG 4.1: WORKING BLOCK DIAGRAM

Automation has revolutionized the world. Today instead of shopkeepers selling items manually, we have automatic machines accepting money and dispensing products. Vending machines are devices where the customers insert coins or credit cards to purchase newspapers, snacks, beverages, tickets, etc. It is the most practical method of purchasing.

Vending machines operate through a combination of electromechanical processes. Initially, the user inputs payment, which is then validated by the machine's internal system, checking for authenticity and value. Once payment is confirmed, the user selects a product via a keypad or touchscreen. This selection triggers an internal mechanism, often involving motors and coils, to release the chosen item.

Sensors within the machine ensure the product has been dispensed correctly, and if not, the system may retry or initiate a refund. Modern machines also incorporate digital technologies, allowing for cashless payments and remote inventory monitoring, thereby providing a very convenient and efficient way for consumers to obtain products.

In the project, we have designed a sequential circuit that dispenses various products when coins are inserted into the machine. The article describes the modeling of the Finite State-based Vending Machine using the mealy model. The code for the vending machine is written in Verilog HDL and simulated in the Model Sim. A finite state machine is an abstract machine that can be in any number of states at any given time. It is a model that describes the synchronous sequential machine. Every sequential circuit has inputs, outputs, and an internal state.

Based on the present state and the present input, the finite state machines can be of two types:

#### 1. MooreFiniteStateMachine

If the next state of the system depends only on the present state, then it is called a Moore Finite State Machine.

### 2. MealyFiniteStateMachine

If the next state of the system depends on both the present state and the present input, then it is called a Mealy Finite State Machine.

The Finite Machine is implemented Mealy State in the project. In this project, we have designed a vending machine that can dispense three products of different prices with additional features of 'return balance' when the money of higher denomination is inserted and 'return money' when the request is cancelled. Any Sequential digital circuit can be converted into a state machine using a state diagram. In a state machine, the circuit's output is a different set of states i.e. each output is a state. There is a State Register to hold the state of the machine. There is a next state logic to decode the next state.

Furthermore, many vending machines now feature temperature control, ensuring perishable items like beverages and snacks are stored at optimal conditions. Advanced models can also display nutritional information and allergen warnings, catering to consumer health needs. Network connectivity allows for real-time sales data collection, enabling operators to optimize product offerings and restock efficiently. Some machines even offer interactive displays, providing advertising and entertainment options. The integration of mobile payment systems and loyalty programs enhances the user experience.

There is also an output register that defines the output of the machine. The next state (ns) logic is the sequential part of the machine. The output and present state (ps) is the Register part.

The products available in the program are as follows.

Newspaper- priced at Rs.5

Cadbury bar- priced at Rs. 10

Tropicana juice- priced at Rs. 15

The buyer can insert money of the following denomination.

Rs. 5

Rs. 10

Rs. 20

The states defined in the design of the vending machine are:

Void State

Five State

Ten State

Fifteen State

As per the money inserted by the buyer, the machine will output the products and change if extra money is inserted.

FIG 4.2: FLOW CHART OF VENDING MACHINE

The flowchart explains the entire process of how the vending machine functions in the program. Initially, the customer must select the product followed by inserting the money. After inserting the money, the machine checks if the cancel button is pressed by the customer. If the customer presses the cancel button, the money is returned to the customer. Else the machine checks the inserted money with the price of the selected product. If both are equal, then the machine dispenses the product. If the inserted money is greater than the price, then the vending machine gives the appropriate product along with the change. If the inserted money is less than the price of the selected product, then the vending machine waits for the customer to insert more money.

The flowchart illustrates the operational logic of a simple vending machine, beginning with the user selecting a product. Subsequently, the user inserts coins, and the machine increments the count of the money received. A decision point is then reached: if the user cancels, the machine returns the money and stops. If not, the machine checks if the inserted money equals the product's price. If it does, the product is dispensed, and the process ends. If the money exceeds the price, the product is dispensed along with the change, and the process concludes. However, if the inserted money is less than the price, the process loops back, prompting the user to insert more coins. This cycle continues until either the correct amount is inserted, a cancellation occurs, or change is dispensed, ultimately leading to the "Stop" state. The flowchart effectively portrays the sequential and conditional steps involved in a basic vending machine transaction.

This flowchart represents a foundational model of a vending machine's transaction process, highlighting the core interactions between the user and the machine. It simplifies the complex electronic and mechanical operations into a series of logical steps, focusing on the user's perspective. The "Select the product" stage initiates the transaction, setting the stage for the payment process. The "Insert coins" and "Increment count" steps form the iterative payment phase, where the machine accumulates the user's input. The inclusion of the "Cancel?" decision point provides the user with an option to terminate the transaction, ensuring flexibility and user control. The "Money = Price?" and "Money > Price?" decision points are critical for determining the outcome of the transaction, distinguishing between exact payment, overpayment, and underpayment scenarios. The loop back to "Insert coins" emphasizes the machine's ability to handle insufficient funds, prompting the user for additional payment. The "Give product" and "Give product and change" actions signify successful transactions, marking the culmination of the process.

# CHAPTER 5 RESULTS

### **5.1 RESULT OF THE PROJECT**

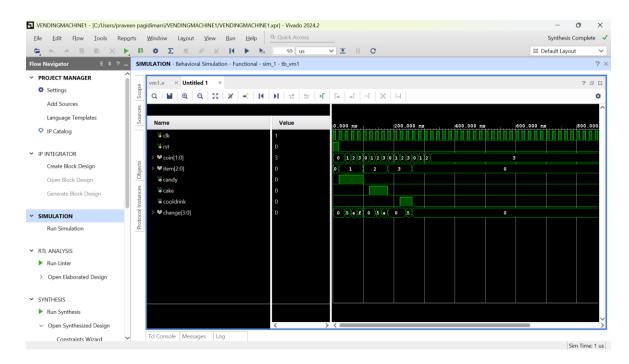

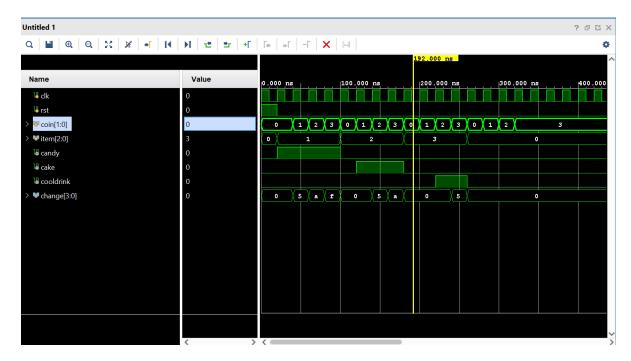

The Verilog testbench (tb\_vm1.v) is designed to verify the functionality of a vending machine module (vm1). It initializes various input signals, applies test cases, and observes the system's behaviour. The testbench first sets the clock (clk) to 1, enables the reset (rst), and initializes the coin and item inputs to zero. The reset is then deactivated to allow normal operation. The vending machine accepts a 2-bit coin input representing different denominations and a 3-bit item input to select different products, including candy, cake, and cooldrink.

The testbench systematically tests each product selection by setting the item input to a specific value and varying the coin input across four different values. The first test case selects candy (item = 3'b001) and applies coin values sequentially to observe if the correct product is dispensed. The same approach is used to test cake (item = 3'b010) and cooldrink (item = 3'b011). Additionally, the testbench verifies the scenario where no item is selected (item = 3'b000), checking if the vending machine correctly handles cases with invalid selections.

FIG 5.1: CASE 1

A clock signal is generated using an always block that toggles the clk signal every 10 time units, ensuring the vending machine operates synchronously.

The testbench provides a comprehensive validation of the vending machine's behavior by simulating various input combinations and monitoring the outputs, including the dispensed product signals (candy, cake, cooldrink) and the returned change (change[3:0]). The simulation results will help determine whether the vending machine logic is functioning correctly.

The provided figure presents a simulation waveform, a crucial tool in digital circuit design, used to visualize and verify the behavior of a circuit over time. The right side of the image displays the waveforms, where the horizontal axis represents time, measured in

nanoseconds, and the vertical axis indicates the value of each signal. The left side enumerates the signals being simulated, including a clock signal (clk), a reset signal (rst), user inputs for item selection (item [2:0]) and coin insertion (coin [1:0]), output signals for item dispensing (candy, cake, cooldrink), and the calculated change (change [3:0]). The waveforms illustrate the dynamic changes in these signal values, allowing designers to observe the circuit's response to different inputs and conditions. For instance, the item and coin signals show user selections, while the dispensing signals and change signal reflect the machine's output. The yellow vertical line at 52.000 ns pinpoints a specific time for detailed analysis. Overall, this simulation waveform serves as a visual representation of the circuit's operation, enabling designers to confirm its functionality and identify any potential issues.

Notably, the waveform includes a clock signal (clk), characterized by its periodic square wave, which serves as the timing reference for the circuit. A reset signal (rst) is also depicted, transitioning from low to high momentarily, indicating an initialization phase. The user's input is represented by the coin [1:0] signal, which cycles through values 0 to 3, likely representing different coin denominations, and the item [2:0] signal, which

**FIG 5.3: CASE 3**

indicates the selected product. The output of the circuit is shown through the candy, cake, and cooldrink signals, which go high when the corresponding item is dispensed, and the change [3:0] signal, displaying the calculated change in hexadecimal format. The yellow vertical line at 146.500 ns marks a specific point in time for detailed analysis. This waveform effectively visualizes the circuit's operation, enabling designers to verify its functionality and timing characteristics.

The figure presents a digital circuit simulation waveform, a visual representation of signal behaviour over time, crucial for verifying the functionality of digital designs. The horizontal axis represents time in nanoseconds, while the vertical axis displays the values of various signals. The simulation includes a clock signal (clk), a periodic square wave essential for synchronizing the circuit's operations. A reset signal (rst) is also present, transitioning briefly to a high state, indicating an initialization phase. The coin [1:0] signal represents user input, cycling through values 0 to 3, likely corresponding to different coin denominations.

The item [2:0] signal indicates the selected item, with values 1, 2, 3, and 0 representing different choices.

The output of the circuit is shown through the candy, cake, and cooldrink signals, which go high when the respective item is dispensed, and the change [3:0] signal, displaying the calculated change in hexadecimal format. The yellow vertical line at 168.000

FIG 5.4: CASE 4

marks a specific time for detailed analysis of the signal values. This waveform allows designers to observe the timing and behaviour of the circuit, ensuring it functions as intended.

The image displays a simulation waveform, a critical tool for verifying the functionality of digital circuits. The horizontal axis represents time, measured in nanoseconds, while the vertical axis shows the values of various signals. The simulation includes a clock signal (clk), a periodic square wave essential for synchronizing the circuit's operations, and a reset signal (rst), which is initially low and briefly goes high for initialization.

The output of the circuit is shown through the candy, cake, and cooldrink signals, which go high when the respective item is dispensed, and the change [3:0] signal, displaying the calculated change in hexadecimal format.

The simulation includes a clock signal (clk), a periodic square wave essential for synchronizing the circuit's operations.

A reset signal (rst) is also present, transitioning briefly to a high state, indicating an initialization phase. The coin [1:0] signal represents user input, cycling through values 0 to 3, likely corresponding to different coin denominations.

**FIG 5.5: CASE 5**